# **Electronic Emission Notices**

#### Federal Communications Commission (FCC) Statement (011128)

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with instructions contained in this manual, may cause harmful interference to radio and television communications. However, there is no guarantee that interference will not occur in a particular installation.

If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- REORIENT OR RELOCATE THE RECEIVING ANTENNA

- INCREASE THE SEPARATION BETWEEN THE EQUIPMENT AND THE RECEIVER

- CONNECT THE EQUIPMENT INTO AN OUTLET ON A CIRCUIT DIFFERENT FROM THAT OF THE RECEIVER

- CONSULT THE DEALER OR AN EXPERIENCED AUDIO/TELEVISION TECHNICIAN

**NOTE:** Connecting this device to peripheral devices that do not comply with Class B requirements, or using an unshielded peripheral data cable, could also result in harmful interference to radio or television reception.

The user is cautioned that any changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate this equipment.

To ensure that the use of this product does not contribute to interference, it is necessary to use shielded I/O cables.

# Copyright

This manual is copyrighted with all rights reserved. No portion of this manual may be copied or reproduced by any means.

While every precaution has been taken in the preparation of this manual, no responsibility for errors or omissions is assumed. Neither is any liability assumed for damages resulting from the use of the information contained herein.

#### Trademarks

All brand names, logos and registered trademarks mentioned are property of their respective owners.

# **Table of Contents**

| HARDWARE CONFIGURATION                    | 3  |

|-------------------------------------------|----|

| Key Features 3                            | 3  |

| Motherboard Layout 5                      | 5  |

| Jumper Settings6                          | ô  |

| JP1 - Host Bus Speed Select6              | ô  |

| J3, J4 - On Board AC97 Codec Sound6       | 6  |

| JBAT1 - CMOS Clear6                       | 6  |

| JP4 - On board LAN6                       | ô  |

| SW1 - VID[0:4] Code to Voltage Definition | 7  |

| Pin Assignment 8                          | 3  |

| HARDWARE SETUP                            | 9  |

| To Install DIMMs                          | 9  |

| Installing a New Processor                | 9  |

| To Install a Processor to ZIF Socket      | 9  |

| Connect the processor Fan Connector 1     | 10 |

| BIOS SETUP 1                              | 10 |

| Starting Setup                            | 10 |

| Main Menu 1                               | 11 |

| Standard CMOS Features 1                  | 12 |

| Advanced BIOS Features 1                  | 13 |

| Advanced Chipset Features 1               | 13 |

| Integrated Peripherals 1                  | 13 |

| Power Management Setup 1                  | 13 |

| PnP/PCI Configurations 1                  | 13 |

| PC Health Status1                         | 13 |

| Frequency/Voltage Control1                | 13 |

| Set Supervisor/User Password1             | 14 |

| Flash Update Procedure                    | 15 |

| APPENDIX 1                                | 16 |

| Select the Heatsink 1                     |    |

| Delect the Heatshirk                      | 16 |

# HARDWARE CONFIGURATION

# **Key Features:**

# Chipset

VIA® VT8361 system controller and VT82C686A/B south bridge.

#### **Processor**

- Full support for the AMD Duron<sup>™</sup> and Athlon<sup>™</sup> processors using Socket A.

- Supports 100MHz & 133MHz bus speed including all processors using Socket A.

### VRM 9.0 (Voltage Regulator Modules) on Board

Flexible motherboard design with on board VRM 9.0.

#### System Memory

- A total of two 168-pin DIMM sockets (3.3V Synchronous DRAM).

- Supports Synchronous DRAM PC100/PC133.

- · Memory size up to 1G bytes.

- · Supports SDRAM memory types.

- Supports single-density DIMMs of 1MB, 2MB, 4MB, 8MB and 16MB depth (x64).

- Supports double-density DIMMs of 2MB, 4MB, 8MB, 16MB and 32MB depth (x64).

- Supports single & double sided DIMMs.

### **System BIOS**

- 2MB flash BIOS supporting PnP, APM, ATAPI and Windows® 95.

- · Auto detects and supports LBA hard disks.

- · Full support of ACPI & DMI.

- Easy to upgrade BIOS by end-user.

#### On-board I/O

- On board two PCI fast IDE ports supporting up to 4 ATA and Ultra DMA33/66/ 100 (optional) IDE devices.

- Supports bus master IDE, PIO mode 4 (up to 16.6M bytes/sec) and Ultra DMA33/66/100 (optional) (up to 33/66/100M (optional) bytes/sec) transfer.

- One ECP/EPP parallel port.

- Two 16550-compatible UART serial ports.

- One floppy port supports two FDDs of 360KB, 720KB, 1.2MB, 1.44MB and 2.88MB capacity.

- Four USB ports.

- · One front panel sound connector.

- PS/2 mouse port.

- PS/2 keyboard port.

- Infrared (IrDA) is supported.

- One Line/Speaker out, one Mic in, one Line in and MIDI/Game port (optional).

# Plug-and-Play

- Supports plug-and-play specification 1.1.

- Plug-and-play for DOS, Windows® 3.X, Windows® 95 as well as Windows® 98.

- Fully steerable PCI interrupts.

## On-board AC97 Sound

- Integrated AC97 controller with standard AC97 codec.

- · Direct Sound and Sound Blaster compatible.

- Full-Duplex 16-bit record and playback.

- PnP and APM 1.2 support.

## **On-board VGA**

- 64-bit single Cycle 2D/3D graphics engine.

- Real time DVD MPEG-2 and AC-3 payback.

- Integrated 24-bit 230MHz RamDAC.

- Resolution up to 1600 x 1200.

- Win95 osr-2 Vxd, integrated Win98/NT5 mini-port drivers support.

### National DP83815 On-board (optional)

- Integrated fast Ethernet MAC, physical chip and transceiver in one chip.

- 10 Mb/s and 100 Mb/s operation.

- Supports 10 Mb/s and 100 Mb/s N-way Auto-negotiation operation.

- · Supports Wake-On-LAN function and Remote wake-up.

- · Supports LED pins for various network activity indications.

- Half/full duplex capability.

- Supports full Duplex flow control (IEEE802.3x).

## **Power Management**

- Supports SMM, APM and ACPI.

- · Break switch for instant suspend/resume on system operations.

- Energy star "Green PC" compliant .

- WOL (Wake-On-Lan) Header support.

- External Modem Ring-in Wake-up support.

- Support auto setting or manual setting for CPU voltage.

#### **Expansion Slots**

- 3 PCI bus master slots (Rev. 2.1 compliant).

- 1 CNR slot. (communication and networking riser) (support communication only, sharing with 1 PCI slot).

#### CAUTION

Static electricity can harm delicate components of the motherboard. To prevent damage caused by static electricity, discharge the static electricity from your body before you touch any of the computers electronic components.

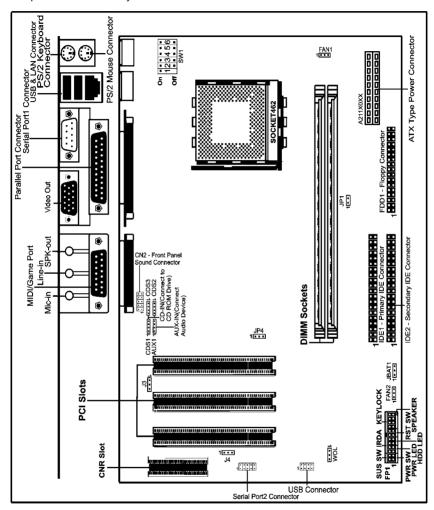

## **Motherboard Layout**

The following diagrams show the relative positions of the jumpers, connectors, major components and memory banks on the motherboard.

# **NOTE**

- Be sure to check the cable orientation in order to match the colored strip to the pin 1 end of the connector.

- When you start up the system, please wait for 5 seconds after you power on AC.

# **Jumper Settings**

This chapter explains how to configure the motherboard's hardware. Before using your computer, make sure all jumpers and DRAM modules are set correctly. Refer to this chapter whenever in doubt.

# JP1 - Host Bus Speed Select

| JP1     |       | CPU Clock Speed |

|---------|-------|-----------------|

| 1 C     | lose* | 100MHz*         |

| 1 • • O | pen   | 133MHz          |

# J3, J4 - On Board AC97 Codec Sound

| J3     | J4          | Function           |  |

|--------|-------------|--------------------|--|

| 1 2-3* | 1 2-3* (S)# | AC97 Sound Enable* |  |

| 1 1-2  | 1 1-2 (P)#  | AC97 Sound Disable |  |

#### JBAT1 - CMOS Clear

| JBAT1  | Selection  |

|--------|------------|

| 1 1-2* | Normal*    |

| 1 2-3  | CMOS Clear |

#### JP4 - On Board LAN

| JP4    | Function             |

|--------|----------------------|

| 1 1-2* | On board LAN Enable* |

| 1 2-3  | On board LAN Disable |

# P = Primary CNR, S = Secondary CNR

SW1 - VID[0:4] Code to Voltage Definition

| SW1[1:6]<br>VID[0:4] | VCC_CORE | SW1[1:6]<br>VID[0:4] | VCC_CORE        |

|----------------------|----------|----------------------|-----------------|

| 1 2 3 4 5 6          | 1.850    |                      | 1.450           |

| 1 2 3 4 5 6          | 1.825    |                      | 1.425           |

| 1 2 3 4 5 6          | 1.800    |                      | 1.400           |

| 1 2 3 4 5 6          | 1.775    |                      | 1.375           |

| 1 2 3 4 5 6          | 1.750    |                      | 1.350           |

| 1 2 3 4 5 6          | 1.725    |                      | 1.325           |

| 1 2 3 4 5 6          | 1.700    |                      | 1.300           |

| 1 2 3 4 5 6          | 1.675    |                      | 1.275           |

| 1 2 3 4 5 6          | 1.650    |                      | 1.250           |

| 1 2 3 4 5 6          | 1.625    |                      | 1.225           |

| 1 2 3 4 5 6          | 1.600    |                      | 1.200           |

| 1 2 3 4 5 6          | 1.575    |                      | 1.175           |

| 1 2 3 4 5 6          | 1.550    |                      | 1.150           |

| 1 2 3 4 5 6          | 1.525    |                      | 1.125           |

| 1 2 3 4 5 6          | 1.500    |                      | 1.100           |

|                      | 1.475    | 1 2 3 4 5 6          | Defaulting CPU* |

SW1(6) Off, Auto Setting SW1(6) On, Manual Setting

On Off

\* =Default setting.